|

LabGuy's World: 'Goldmark 1' - Field Sequential Color TV Project

PART SIX: Time to sort the wheat from the chaffe. We need to isolate red sync, generate the six field ramp voltage and detect the presence of video.

Schematic diagram and a photo of the Video Buffer and Sync Separator 20130716 This section is now working. The plus and minus five volt regulators are in the lower left of the schematic. These provide low voltage for the op amps and the digital logic. One op amp, of four total, is wired as a unity current buffer. The output is split in two. The output jack goes to the CRT monitor, to be added (or even designed and built from scratch!) at a later time. Notice the repaired op amp on the adapter board to the left of the yellow jack. The red wire is plus five volts power. The green wire is minus five volts. Each yellow wire is an op amp negative input pin. Last, but not least, the four pin header next to U2, the LM1881N sync separator, is a handy place to pick off sync test signals with the oscilloscope. In the last photo, you can see the surface mount resistors and capacitors if you look close enough. The way the 0603 size resistors and capacitors fit between the 100 mil pads is excellent! The old addage about 'keep the leads as short as possible' has been taken to a completely new level.

Scope shot of the vertical sync interval and CBS format FCC Waveform 20130717 Above we see the CBS vertical interval on the bottom trace and separated vertical sync on top. Detail 1 is the little devil we seek! The red sync appears between these two equalizing pulses every three fields. There is a tiny difference between the red sync in each field. This will make my pulse timing process harder, should I choose to go that way. That is, if I desire to detect both color sync pulses. But, we really only need the "first" red sync pulse. This is the red sync occuring in the odd video field, vs the even field. This is the one I will lock my color wheel to at the 24 revolutions per second rate. Detail number 2 is the falling edge of vertical sync in the composite waveform. Detail 3 is called serrations. Detail 4 are equalizing pulses. The equqalizer and serration pulses occur at twice the horizontil rate. They are a legacy going back to the days of vacuum tubes and AC coupled circuits in a Hi-Z environment. (Solid state tech is what we scientists consider a "low Z" environment.) These pulses kept the video signal from "humping" in the vertical interval when it crosses a series capacitor. I intend to descriminate the red sync via a digital "pulse counting" techniques. I use mostly DC coupling in my video circuits, so these pulses are technically not needed in this design. You can see the vertical interval is flat as a board in this case. Detail 5 does not exist. Detail 6 is resumption of horizontal sync at 29.160KHz / 41.67uS. Details 7 & 8 respecitvely are the falling and rising edges of the vertical sync pulse recovered by the LM1881N.

The [Aurora Design] World Converter Model WC-01 The CBS video signal is being generated by my Aurora Design WC-1, World Converter. A little box that takes in standard def video and converts it to many obsolete historical television standards, both electronic and mechanical. This was the reason I purchased it, despite the high price. Without this tool, there is no project. As far as I know, this is the ONLY modern source of some of these old formats. Especially, the CBS 405/72i format we will be using here.

Assembly photos - Low voltage regulators and TTL logic sockets 20130717 In the first photo we see the plus and minus five volt regulators. They don't require large heat sinks because I will be using a lot of CMOS logic and power consumption there is almost zero. The op amps uses literally all the power being pulled from the two regulators. And, that's not very much either. In the center, I have preinstalled some IC sockets for experimenting. The power pins and ground pins are wired in advance. I show in detail how the ground works with machined pin sockets and this board material. That is a guaranteed solid ground connection for that chip. This circuit board material, known as 'vector board', is manufactured by [Twin Industries], [P/N 8100-4565]. This material is available in other sizes as well. Not cheap stuff, Maynard. But, worth every centavo! I get almost all of my electronic prototyping materials from Anchor Electronics in Santa Clara, California. Best prices, awesome service. Virtually every part on this board came from Anchor. Thanks Anchor! The last photo shows the entire path of the plus and minus five volt rails. Red is +5V, green is -5V. The left most chip is wired up for experimenting. Good news, everybody! The video detect signal is working and will feed a single transistor to drive the power amp relay. This is the mechanism that starts the motor and turns on the CRT monitor only when a video input is present. The composite sync stream goes to the input of a retrigerable timer (one shot, monostable multivibrator, dual, 74HC123). As long as there are pulses present, the output of timer stays on. It will stay on for the time interval after the last pulse if the video were to stop. And last, the marker pen was used liberally to make my old crossed eyes hit those pins easier. On the construction side, the detail shows the 0.1uF (100nF) capacitors soldered to the VCC pins of the chips. Not shown, is when I run a small wire through the hole at the other end of the capcitor. On top of the board, this wire is bent over, clipped off, and soldered solidly to the ground plane. It is common construction practice to bypass every power line, with a high frequency capacitor, where it enters a chip. This capacitor provides a direct path to ground for any noise signals that may be hitching a ride on our DC power lines. You can not use too many bypass capacitors! When in doubt, stick one in. It can't hurt. More tomorrow, no doubt!

Schematic, waveform and PCB addtions of Red Sync Detector Window Circuit 20130718 Here's my "first order" digital solution to the red sync window generator. No doubt, this is oversimplified at this time. But, we are on the right path. The output of this will need just a tiny bit more conditioning. But, the hard part is done. The 74LS592 is an 8 bit counter with data preload. When the "Counter Load" pin pulses low, on the falling edge of vertical sync, the dip switch value is loaded into the counter. It then counts up from that value until it rolls over to zero. When the count goes over the top, the ripple carry output (RCO) goes low for one count. The counter load pulse is created by drastically shortening vertical sync to far less than one line period of 34.3uS. This is so that counting starts on the very next available pulse, which happens to be the first serration pulse in vertical sync. As a 405 line system, there are only 202.5 lines in a field. An 8 bit counter can handle this range because even counting equalizer and serration pulses with the horizontal sync pulses, we still get less than 256 counts! NO NEED to separate horizontal sync and one of my favorite counters can do the job! Woo hoo! We are not 100% done yet. This counter only generates a window of time that surrounds the red sync pulse location. Notice the timing diagram, lower left on the schematic. I did not use the rising edge of vertical sync because it is not stable and jitters by half a line. The next step is to gate the comp sync with this pulse to extract only the active red sync pulse. Standby for that tomorrow.

ABSOLUTE Red Sync Detector Circuit and 6 field ramp waveform 20130720 ATTENTION: My descriptions are intentionally over simplified. Irrelevant details will be omitted. Since last session, I went back and took a closer look at both -VS (vertical sync not) edges. It matters which edge you choose to trigger your o'scope with. A classic simple error. I have bias to choose the falling edge. Because, in traditional TTL digital logic, the falling edge was the more stable of the two. It was not in this case. Taking that closer look, I discovered that the rising edge of vertical sync, coming out of the LM1881N, is the stable reference after all. It also does not occur on a sync or equalizer pulse edge. This means I can use it as a way to block counting the serration pulses and a few other edges in the vertical sync region. Now the 8 bit counter counts mostly horizontal sync pulses and only the first one or two equalizer pulses. When there are two equalizers, and before the timer is reset, the second one is red sync! I had this brainstorm this morning and jumped right on this. I found that the LM1881 vertical sync rising edge made fine enable signal to the counter chip. This eliminated the need to count serration pulses in the vertical sync interval. The rising edge of vertical sync was a perfectly stable point in time, occurring precisley every 202.5 scan lines apart. The falling edge of vertical sync is actually dithering by half a line in each field. In other words, it was a stable point for us to begin counting from. From this point we literally count horizontal sync and only a few equalizing pulses as we leave active video and go into the next vertical interval. The counter starts at 52 decimal and counts up from there. Eight bit counters roll over to zero after counting to 255. (2^8-1) The counter is reloaded with this preset value on each vertical sync. When the count reaches 255, the RCO pin pulses low. I set the count preload value such that it is one count short of the top when vertical sync hits again. But, in a field with a red sync pulse, the count overflows just before vertical sync. Perfectly locked to the red sync in the first field of the six field cadence. 255 - 52 = 203, the nearest decimal value greater than 202.5. That's the total number of pulses when -VS is high. From there, the RCO pulse fires a timer, U2 that stretches the pulse out long enough for the 10uF capacitor to fully discharge to zero volts. The timer turns on the FET switch Q3 to discharge the capacitor and turns off to let the ramp rise until the next red sync pulse. This capacitor now charges for the remainder of 1/24th of a second. The current source is set by the value of R1. The 604 ohm resistor sets Ki to approximately 1mA. This ramp voltage is buffered by the op amp and will go to the next stage, sampling. That's the last step before closing the servo loop and turning it on! CONSTRUCTION DETAIL

Two 2N3906 PNP transistor comprising the constant current source Ki. A quick look at how I bonded the two transistors together so they will track each other over temperature. A dab of heat sink grease on the flat sides and a small wrapper of heat shrink tubing. In the schematic, there is a detail on the construction of this circuit. It's easy to make and very useful. I always use yellow for positive current sources and green shrink tubing for negative current sources, using the complimentary 2N3904 NPN transistor.

Final circuit completed and under going initial testing 20130721 Testing was not gratifying. The motor was prone to fits and starts. The optical tach seemed to be working as expected however. The power amplifier was throwing off some fierce heat. Investigating farther, I discovered that something in the circuit is oscillating at a few kilocycles. Rats! Will get back to you once the amplifier oscillation is neutralized. (Update 20130724) Here is my conclusion about what happened. The way I have the servo now, it would only work if the motor was already running at the right speed. It cannot start from a dead stop. How do you fix this? It is straight forward. Recalling the testing of the motor amplifier, when I was driving the input with simple potentiometer. This is a speed control. So, the solution is to split the input of the motor drive amplifier into two parallel paths, one sets the speed, the other the phase. The phase part is built. The speed part is the good old 5K potentiometer! This is routed to the MDA input through a series 1K resistor. The output of the phase detector is routed to the same MDA input through a 9K resistor. This divides the control responsibility 90/10 between the speed and phase servo. Now the phase servo has a much smaller effect on the instantaneous speed of the motor. Stay tuned as I test this theory. (Resume 20130721) To debug the two timers in the photo tach path, I substituted the red sync pulse via a handy selector just before the first timer. It is the right frequency and pulse width. This allowed me to pick capacitors until I had the control range I was seeking. The phase timer is capable of 5mS to 40mS, which is plus and minus 170 degrees in terms of phase. This is an overkill phase control! Excellent. I was able to use this test pulse to check the sample and hold circuit as well. Turning the phase control, the sample pulse moves from the left end of the ramp all the way to the right. With the o'scope connected to the sample voltage test point TP-2, The DC voltage tracked the sample point on the ramp perfectly. When the sample pulse is steady and locked in the center of the ramp, the sampled voltage will be just about 2.5 volts. I discovered an issue with the 74HC221 timer ICs that I like to use. The resistor must never be less than 1K or bad things happen. Heat, stink and smoke. Yep. A 1K resistor was installed in series with the 50K pot to set the bottom end.

SUCCESS! The servo is locked perfectly. Schematics so far. 20130725 Splitting the input currents to drive the motor amp worked. In implementing this change, the oscillating op amp was eliminated altogether. The power amp runs barely warm to the touch now. The plus five volt regulator is not so lucky. That one gets a larger heat sink or a tiny fan. Entered the schematics into cad tonight. Posted the first order copies with my mark ups and all. Thanks to my new oscilloscope, we can see up to four traces at once. The first trace is the ramp waveform, derived from video. The green trace is the delayed and reshaped pulse that is produced when the motor is turning. Trace three is the output of the phase detector and it is actually zero volts because there is currently zero phase error. The bottom trace in blue is the undersampled video waveform. There is nothing wrong with the video, this is a sampling artifact that is normally seen on digitizing oscilloscopes. Who doesn't enjoy a good dose of sweet irony now and then? Ok, you can leave. The rest of us love it! This new o'scope I purchased on July 24, is a Tektronix TDS-744A. A four channel 500MHz digitizing scope with color display. There is nothing unusual about that. However, in this case, Tektronix channeled Dr. Peter Goldmark a few years ago and produced the coolest display to date. It uses a white phosphor monochrome CRT and a special RGB switching liquid crystal shutter. The irony is that this scope uses a "field sequential color television display"! And to think, that I told my agent the features I wanted in a new scope, and my budget, and he produced this scope at random... to help me build a field sequential color TV. Now, that's karma! 20130726

Color wheel phase range test: [-26mS] - [0] - [+22mS] Testing and final touches continue. In this test, we trigger the scope on the falling edge of ramp, which is coincident with red sync. The green trace is the retimed sample pulse derived from the photo tach, TP-6. It will always appear at the center of the ramp, as that is the lock point. We will observe the actual photosensor signal on the bottom, yellow, trace. Relative to the falling edge of the sync, we can move the wheel back by 16mS and forward by 24 ms. A range of 40mS total. The period of the ramp is 41.667mS, the reciprical of 24Hz. When the second trace pulses low, that is the moment when the sample and hold circuit takes a voltage "snap shot" of the ramp and stores it on C25. This pulse is as short as possible. Mostly limited by the minimum time the switch, U10-A, will fully turn on and turn off. Voltage divider, R35, R36, supplies a 2.5 volt reference to the op amp U8-B. U8-B is running at a gain of +2 and then the output is divided by a pot to find the best set point. The pulse phase error voltage is going to move the sample point until it coincides with the 2.5 volt point on the ramp.

Latest schematic 20130726 Completed the video presence detect circuit that turns on power to the amplifer only when video is present. It is labeled, "power amp control", on the schematic. This circuit saves wear and tear on the wheel motor as there is no reason for it to spin if there is no TV signal. Same for the video monitor which is also power controlled by this same circuit. I tried to group the functions into distinct blocks for anyone who needs one of these functions. I hope this becomes the reference design for old fasioned analog DC motor servos. I chose this style of servo because it is a nostolgic look back at VTR head scanner and capstan servos of the 1960s and 70s. I am currently rewriting the schematics and reorganizing the reference designators. So, don't get too close to these schematics. A final finalized version is in the works.

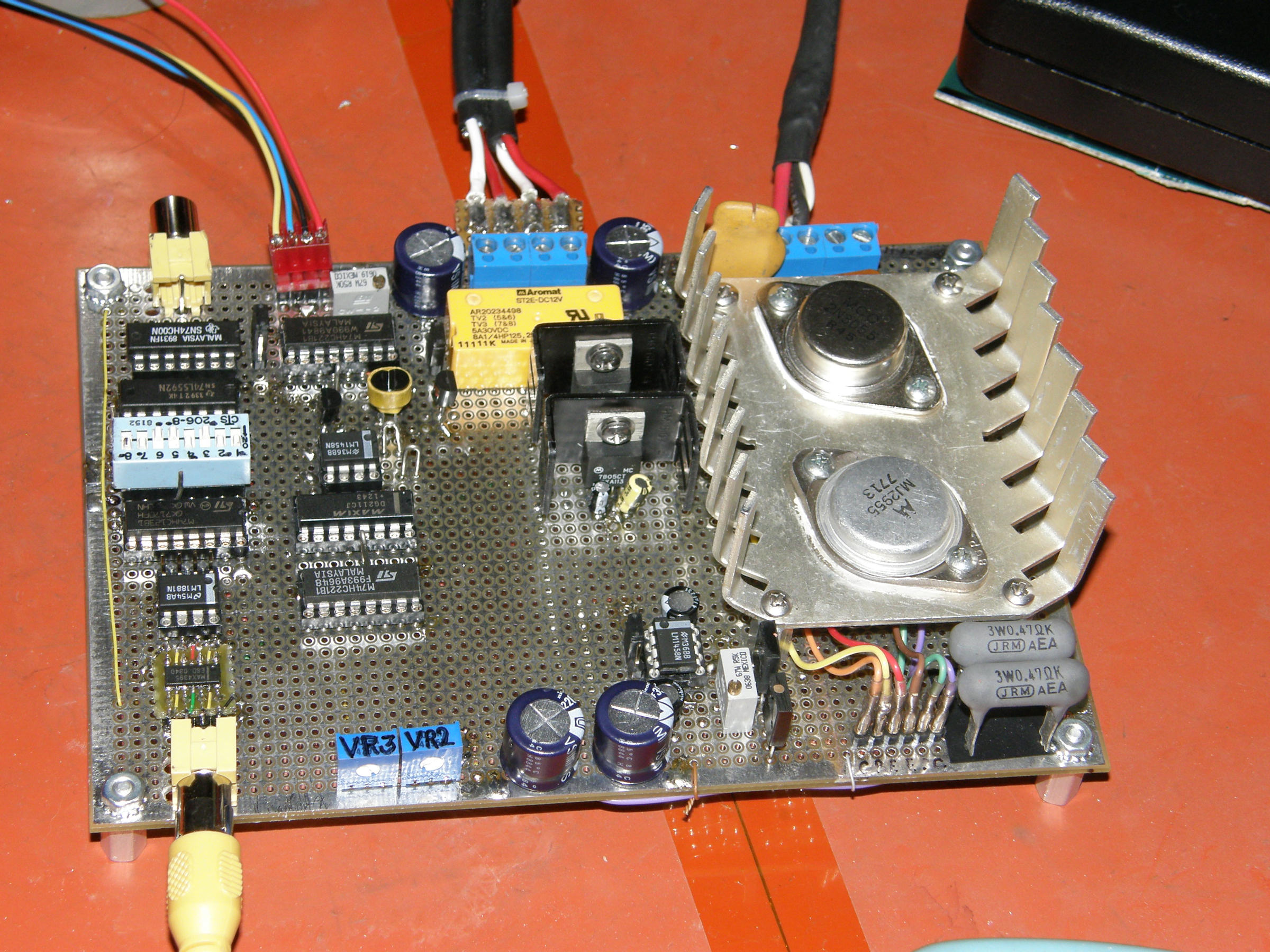

The completed CBS Field Sequential Color Television Servo board and a nice parting shot Here a couple of glamour shots of the servo board and the new o'scope. For a while, I worried there would not be sufficient space on the board for everything. I believe part of the compactness of this design was the liberal use of surface mount passive components. They are hidden on the bottom and are magnificently tiny when compared to older leaded components. I do use leaded parts here and there when their surface mount counterpart is too much trouble to mount to the board. The video op amp, U1, is a good example of this. I had to use that package size because that part was not available in a classic 100 mil DIP package. Since the machining of the spindles and color wheel discs was not completed today, I will return to working on the three inch TV monitor I plan to use in this design. I have many thoughts on how to procede there. It turned out to be a tougher nut to crack than I was expecting. Stay tuned for part 7! [HOME] [ELECTRONICS PROJECTS] [GOLDMARK 1, TOP] [GOLDMARK I, PART 7] Created: July 17, 2013, Last updated: August 3, 2013 |